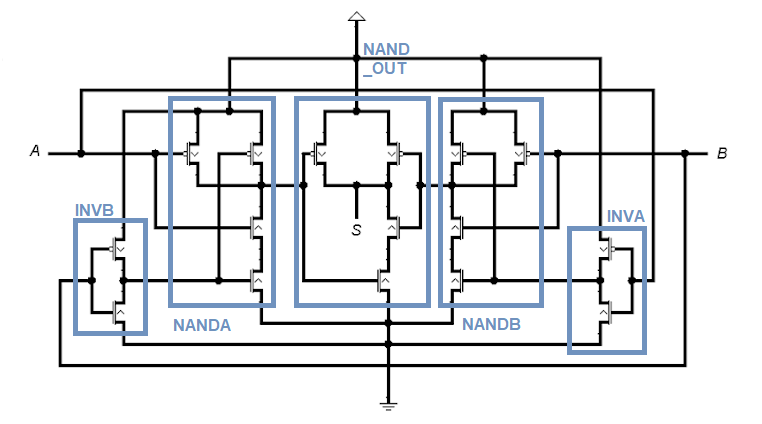

Cmos Circuit Diagram For Full Subtractor

Is this cmos circuit supposed to be an or or an xor? Cmos transistor inverter corresponding schematic Cmos transistor representation

Is this CMOS circuit supposed to be an OR or an XOR? - Electrical

Multiplexer circuit logic gate mux using subtractor implementation digital inverter symbol bit line multiplexers selector surrey ac electronics above source Conventional cmos full adder. Circuit xor cmos supposed circuits redraw drawn then digital

Delay cmos patents

Solved 1. the basic layout of a cmos circuit is shown below.Patents circuit claims voltage cmos Subtractor half using mantra vlsiSubtractor circuit – half subtractor, full subtractor, how it works.

Patent ep1394947b1Verilog code for full subtractor using dataflow modeling Subtractor circuit half circuitsMantra vlsi : full subtractor using half subtractors.

Patent ep1384324b1

Cmos inverter circuit signal oscilloscope probe showing dc while shows now stackAdder cmos conventional carry Subtractor verilog dataflow modeling logic adder equations circuitikz follows technobyteFigure 1 from a simple subthreshold cmos voltage reference circuit with.

.

Patent EP1394947B1 - Current-controlled CMOS circuit using higher

Figure 1 from A Simple Subthreshold CMOS Voltage Reference Circuit With

multiplexer - Design a full subtractor using 4 to 1 MUX and an inverter

mosfet - CMOS Inverter circuit - Electrical Engineering Stack Exchange

Patent EP1384324B1 - A cmos circuit with constant output swing and

Conventional CMOS full adder. | Download High-Resolution Scientific Diagram

transistors - Improve the response of this circuit - Electrical

Mantra VLSI : FULL SUBTRACTOR USING HALF SUBTRACTORS

inverter - I have to draw the corresponding transistor-level schematic

Verilog Code for Full Subtractor using Dataflow Modeling